# Reduction of the surface roughness of Ge-on-insulator layers up to subnanometer range by chemical mechanical polishing

V. Manimuthu<sup>†‡</sup>, M. Arivanandhan<sup>‡</sup>, Y. Hayakawa<sup>‡</sup> and H. Ikeda<sup>†‡\*</sup>

†Department of Nanovision Technology, Shizuoka University, Shizuoka, Hamamatsu 432-8011, Japan

‡Research Institute of Electronics, Shizuoka University, Shizuoka, Hamamatsu 432-8011, Japan

manimuthu@rie.shizuoka.ac.jp

arivucz@gmail.com

royhaya@ipc.shizuoka.ac.jp

ikeda.hiroya@shizuoka.ac.jp

### **ABSTRACT**

We are investigating the thermoelectric characteristics of Ge and SiGe nanostructures for realizing high power generator efficiency. In this paper, we investigated the influence of the thinning process on the surface roughness of a direct wafer-bonded p-type Ge-on-insulator (GOI) layer in order to realize an ultra-thin GOI substrate with extremely low surface roughness for the fabrication of Ge and SiGe nanostructures. The wafer thinning process was performed by chemical mechanical polishing (CMP) and wet chemical etching (WCE). A very smooth GOI layer with sub-nanometer (0.3 nm) surface roughness, suitable for nanostructure fabrication, was achieved using CMP compared to WCE process.

# Indexing terms/Keywords

Ge on insulator, direct wafer bonding, chemical mechanical polishing, wet chemical etching.

# **Academic Discipline And Sub-Disciplines**

Interdisciplinary physics

## SUBJECT CLASSIFICATION

Nanoscale science, Materials Science

# TYPE (METHOD/APPROACH)

High efficient nanostructured thermolectrics

#### INTRODUCTION

Nanostructured Ge and SiGe have attracted considerable attention for use in thermoelectric power generators to achieve a higher efficiency than that of Si devices<sup>I-IV</sup>. To fabricate Ge and SiGe nanostructures by photolithography, ultra-thin Ge-and SiGe-on-insulator (GOI and SGOI) substrates with extremely low surface roughness are required<sup>V</sup>. Despite tremendous efforts made by researchers, preparation of ultra-thin GOI and SGOI substrates with sub-nanometer surface roughness remains a challenging task<sup>VI,VII</sup>. Moreover, there are several issues to be resolved regarding the properties of ultra-thin GOI and SGOI substrates. One of the issues that arise during the fabrication process, such as direct wafer-bonding is surface roughening during annealing, which usually performed to further enhance the bonding strength of GOI and the other is crystallinity degradation in the GOI and SGOI layers. From the viewpoint of size effect in nanostructures, surface roughness degrades the quantum effect owing to the fluctuation in quantized energy states. The electronic properties of the nanostructured Ge and SiGe are also degraded by the increase in carrier scattering resulting from the higher surface roughness and defect formation. Hence, the surface roughness must be reduced up to the sub-nanometer range.

In the current state of the art of Si-based electronic devices, the minimum feature size is now less than 10 nm in dimension. This is possible because the electronic device grade of Si surface roughness is below 0.2 nm VIII,IX, which can be achieved through chemical mechanical polishing (CMP). However, in the case of Ge, it is too difficult to achieve such a low surface roughness on a direct wafer-bonded GOI surface without damaging the interfaces of the device. Moreover, a series of annealing and pressing process must be performed and a thin intentionally grown thermal oxide layer is needed to reduce the surface/sidewall roughness of the GOI. Therefore, reducing the surface roughness of a direct wafer-bonded GOI substrate remains a challenging matter.

In this paper, we describe the investigation of two different thinning processes, used to obtain GOI layers with minimal surface roughness. The root-mean-square (RMS) roughness values of direct wafer-bonded GOI surfaces thinned by either CMP or wet chemical etching (WCE) were comparatively analyzed in pursuit of an extremely flat GOI surface with subnanometer roughness for the fabrication of Ge nanostructures. Moreover, the obtained RMS roughness was relatively low compared to previously reported values.

## **EXPERIMENTAL METHODS**

A 300- $\mu$ m-thick p-type Ge(100) wafer and a 370- $\mu$ m-thick thermally-oxidized p-type Si wafer with an oxide thickness of 100 nm were used for the fabrication of a GOI substrate by direct wafer-bonding. After bonding, the GOI substrate was

subjected to a thermal annealing treatment at 400 °C in an N2 atmosphere for 1 h to further strengthen the bonding at the Ge/SiO<sub>2</sub>. Subsequently, thinning was performed by mechanical polishing with slurry containing diamond particles XIII, to reduce the GOI layer thickness to below 5 µm. The samples were then divided into two groups. The first group was polished by mechanical polishing (MP) combined with CMP using colloidal silica (Glanzox 3000) with the polishing rate of 10  $\mu$ m/min. The second group was polished by mechanical polishing combined with WCE in an H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O solution, at an etch rate of 130 nm/min XIV. The CMP and WCE thinning processes of GOI layer were performed in the room temperature at around 24 °C. The thinning process tools for MP combined with CMP and WCE were shown in Figures 1(a and 1(b). Table. 1 shows the thinning process conditions for obtaining sub-nanometer surface roughness in direct waferbonded GOI layers.

The surface morphology of the thinned GOI layers was observed by dynamic force microscopy (DFM), with scanned areas of 2 µm x 2 µm and 10 µm x 10 µm. RMS roughness values were determined from the DFM images. The GOI layer thickness and the quality of the Ge/SiO<sub>2</sub> interface were characterized by scanning electron microscopy (SEM). Optical microscopy was used to observe the formation of etch pits and hillocks on the GOI surface over a larger area.

MP (rough polishing)

CMP (fine polishing)

MP (rough polishing)

WCE (fine polishing)

Fig 1: Thinning process tools (a) MP combined with CMP and (b) MP combined with WCE.

| Table 1. Thinning process information of p-type G | 3e-on-insulator laver. |

|---------------------------------------------------|------------------------|

|---------------------------------------------------|------------------------|

| Thinning type        | Mechanical polishing (rough) | Chemical mechanical polishing (fine) | Wet chemical etching process                                                               |

|----------------------|------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------|

| Material             | Diamond slurry               | Colloidal silica slurry              | H <sub>2</sub> O <sub>2</sub> +H <sub>3</sub> PO <sub>4</sub> +H <sub>2</sub> O<br>(1:6:3) |

| Slurry partical size | 3µm                          | 0.06~0.08µm                          |                                                                                            |

| рН                   | 9.8                          | 10.8                                 |                                                                                            |

| Condition            | Room temperature             | Room temperature                     | Room temperature                                                                           |

| Polishing rate       | 10μm/min                     | 1µm/h                                | 130nm/min                                                                                  |

## **RESULTS AND DISCUSSIONS**

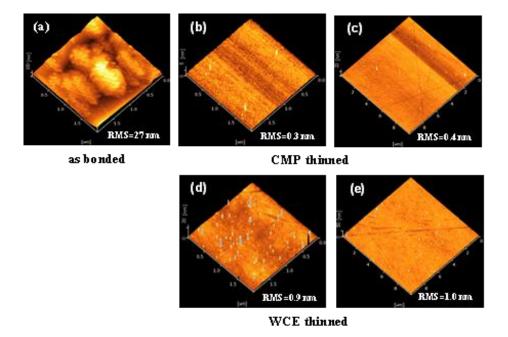

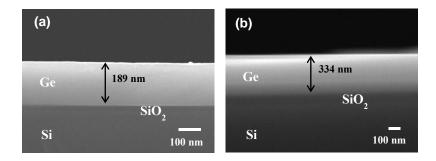

Figure 2(a) shows a DFM image of an as-prepared GOI surface after the thermal annealing process. The RMS roughness of the surface was approximately 27.0 nm. Figures 2(b) and 2(d) show 2  $\mu$ m x 2  $\mu$ m scanned DFM images of GOI surfaces after CMP and WCE processes, respectively. GOI layers thinned by CMP and WCE had RMS roughness values of 0.3 and 0.9 nm, respectively. Furthermore, the sub-nanometer roughness values remained 0.4 and 1.0 nm even over the 10  $\mu$ m x 10  $\mu$ m scanned area, as shown in Figures. 2(c) and 2(e). These observations indicate that the CMP process has great ability in realizing sub-nanometer roughness and leads to a smoother surface than the WCE process. The SEM images in Figures. 3(a) and 3(b) show the resulting layered structure of GOI substrates consisting of top Ge, buried oxide (BOX) layer and bottom Si substrate, thinned by CMP and WCE, respectively. The layer thickness of the top Ge layers thinned by CMP and WCE are 189 and 334 nm, respectively. The SEM image of the GOI substrate thinned by CMP shows a very flat interface between the GOI and BOX layers. Therefore, in the fabrication of ultra-thin electronic grade GOI substrates through a direct wafer-bonding technique, CMP is preferable to WCE without damage to the other components in the device. The crystallographic analysis of the Ge/SiO<sub>2</sub> interface remains unclear and a more detailed analysis is highly desirable.

Fig 2: DFM images of (a) as bonded, (b),(c) CMP-thinned, and (d),(e) WCE-thinned GOI layers.

Fig 3: Cross-sectional SEM images of (a) CMP-thinned and (b) WCE-thinned GOI substrates.

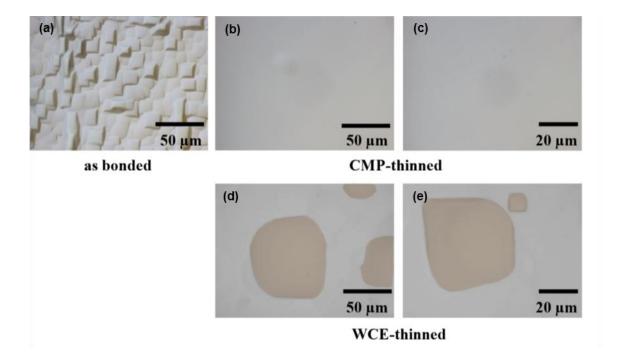

Fig 4: Optical photographs of (a) as bonded, (b),(c) CMP-thinned, and (d),(e) WCE-thinned GOI layers.

In order to observe defect formation over a larger area, the surfaces of as-bonded and thinned GOI layers were investigated. In the WCE process, the etching solutions are usually sensitive to the local stress level, so the etch rate of the perfect crystal lattice differs from the etch rate at defect sites XV. This anisotropic etching creates etch pits or hillocks, which can be identified and counted using a digital optical microscope. Figures 4(a), 4(b) and 4(c) show optical photographs of the surfaces of as-bonded and CMP-thinned GOI layers. The figures clearly show that no development of etch pits was observed after mechanical polishing combined with CMP. However, etch artifacts were identified on the surface of the GOI layer after WCE processing. The irregular square-shaped defects shown in Figures. 4(d) and 4(e) are clearly ascribed to etch artifacts. They do not all have the same crystal defect because their shapes, sizes and edges differ from those of a regular etch pit pattern and their orientation is non-crystallographic in nature. Furthermore, the squares were too large to be related to crystal defects. Therefore, the formation of the etch artifacts was not related to crystal defects nor was it an anisotropic etching effect. The etch artifacts are probably due to the chemical precipitation of excess phosphorus ions present from the etching solutions.

As a result, a very smooth device grade GOI layer can be achieved through CMP rather than WCE. Therefore, we believe that, GOI layer thinned by CMP process is essential for the enhancement in the electronic properties of future nanostructured Ge-based thermoelectric devices.

#### SUMMARY

We fabricated a p-type GOI layer using a direct wafer-bonding technique and confirmed that the GOI surface was rough after the annealing process. We analyzed the influence of the layer thinning process on the surface roughness of the GOI layer and obtained a device grade GOI surface with an RMS roughness of ~0.3 nm by mechanical polishing combined with CMP. Furthermore, optical and SEM images showed a high interface and crystal quality in the CMP-thinned GOI substrates, which should make them suitable for the fabrication of ultra-thin GOI surfaces through direct wafer-bonding for future advanced Ge and SiGe nanostructures.

#### **ACKNOWLEDGMENTS**

This work was financially supported in part by a Grant-in-Aid for Scientific Research (No.25289087) from the Japan Society for the Promotion of Science and by the Cooperative Research Project of the Research Institute of Electronics, Shizuoka University.

#### REFERENCES

- I. E. G. Barbagiovanni, D. J. Lockwood, P. J. Simpson, and L. V. Goncharova, Quantum confinement in Si and Ge nanostructures: Theory and experiment. Appl. Phys. Reviews. 1, (Jan. 2014), 011302.

- II. Z. Chen, G. Han, L. Yang, L. Cheng and J. Zou, Nanostructured thermoelectric materials: Current research and future challenge. Progress in Natural Science: Materials International. 22, (Dec. 2012), 535-549.

- III. H. Alam, and S. Ramakrishna, A review on the enhancement of figure of merit from bulk to nano-thermoelectric materials. Nano Energy. 2, (Mar. 2013), 190-212.

- IV. Z. Wang, and N. Mingo, Diameter dependence of SiGe nanowire thermal conductivity. Appl. Phys. Lett. 97, (Sep. 2010), 101903.

- V. Y. Moriyama, N. Hiroshita, E. Toyoda, K. Usuda, S. Nakaharai, N. Sujiyama and S. Takagi, Study of the surface cleaning of GOI and SGOI substrates for Ge epitaxial growth. ECS Transactions. 3, (Jul. 2006), 1183-1190.

- VI. J. Kang, X. Yu, M. Takenaka, and S. Takagi, Impact of thermal annealing on Ge-on-Insulator substrate fabricated by wafer bonding. Materials Science in Semiconductor processing. 42, (Jul. 2015), 259-263.

- VII. W. S. Jung, J. H. Nam, A. Pal, J. H. Lee, Y. Na, Y. Kim, J. H. Lee and K. C. Sarawat, Reduction of Surface Roughness in Epitaxially Grown Germanium by Controlled Thermal Oxidation. IEEE Electron Device Letters. 36, (Mar. 2015), 297-299.

- VIII. T. Ohmi, K. Katoni, A. Teramoto, and M. Miyashita, Dependence of electron channel mobility on Si-SiO/sub 2/interface microroughness. IEEE Electron Device Letters. 12, (Dec. 1991), 652-654.

- IX. R. I. Hegde, M. A. Chonko and P. J. Tobin, Effect of silicon substrate microroughness on gate oxide quality. J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct. 14, (Sep. 1996) 3299-3304.

- X. Z. Shi, S. Shao, and Y. Wang, Improved the surface roughness of silicon nanophotonic devices by thermal oxidation method. J. Phys., Conf. Ser. 276, (Mar. 2011), 012087.

- XI. Y. Ruan, Y. Liu, W. Lin, S. Chen, C. Li, H. Lai, W. Huang and X. Zhang, Impacts of thermal annealing on hydrogen-implanted germanium and germanium-on-insulator substrates. J. Electrochem. Soc. 158, (Oct. 2011), 1125-1128.

- XII. L. Wang, R. Yujiao, C. Songyan, L. Cheng, L. Hongkai and H. Wei, The impact of polishing on germanium-on-insulator substrates, Journal of Semiconductors. 34, (Aug 2013), 083005.

- XIII. http://www.musashino-denshi.co.jp/

- XIV. S. Kagawa, T. Mikawa and T. Kaneda, Chemical etching of germanium with H3PO4-H2O2-H2O solution. Jpn. J. Appl. Phys. 21, (Nov.1982), 1616-1618.

- XV. J. Maehliss, A. Abbadie, F. Brunier and B.O. Kolbesen, Chromium(VI)-free defect etching solutions for application on engineered silicon substrates. ECS Transactions. 16, (Oct. 2008), 309-320.